# **UltraSPARC Virtual Machine Specification**

(The sun4v architecture and Hypervisor API specification)

Revision 1.0

Please send comments and queries to: hypervisor@sun.com

Copyright 2006 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, California 95054, U.S.A. All rights reserved.

Sun Microsystems, Inc. has intellectual property rights relating to technology that is described in this document. In particular, and without limitation, these intellectual property rights may include one or more of the U.S. patents listed at http://www.sun.com/patents and one or more additional patents or pending patent applications in the U.S. and in other countries.

This document and the product to which it pertains are distributed under licenses restricting their use, copying, distribution, and decompilation. No part of the product or of this document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any.

Third-party software, including font technology, is copyrighted and licensed from Sun suppliers.

Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and in other countries, exclusively licensed through X/Open Company, Ltd.

Sun, Sun Microsystems, the Sun logo, Java, AnswerBook2, docs.sun.com, and Solaris are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and in other countries.

All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and in other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

The OPEN LOOK and Sun? Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees who implement OPEN LOOK GUIs and otherwise comply with Sun's written license agreements.

U.S. Government Rights-Commercial use. Government users are subject to the Sun Microsystems, Inc. standard license agreement and applicable provisions of the FAR and its supplements.

DOCUMENTATION IS PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

Copyright 2006 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, Californie 95054, Etats-Unis. Tous droits reserves.

Sun Microsystems, Inc. possede les droits de propriete intellectuels relatifs a la technologie decrite dans ce document. En particulier, et sans limitation, ces droits de propriete intellectuels peuvent inclure un ou plusieurs des brevets americains listes sur le site http://www.sun.com/patents, un ou les plusieurs brevets supplementaires ainsi que les demandes de brevet en attente aux les Etats-Unis et dans d'autres pays.

Ce document et le produit auquel il se rapporte sont proteges par un copyright et distribues sous licences, celles-ci en restreignent l'utilisation, la copie, la distribution, et la decompilation. Aucune partie de ce produit ou document ne peut etre reproduite sous aucune forme, par quelque moyen que ce soit, sans l'autorisation prealable et ecrite de Sun et de ses bailleurs de licence, s'il y en a.

Tout logiciel tiers, sa technologie relative aux polices de caracteres, comprise, est protege par un copyright et licencie par des fournisseurs de Sun.

Des parties de ce produit peuvent deriver des systemes Berkeley BSD licencies par l'Universite de Californie. UNIX est une marque deposee aux Etats-Unis et dans d'autres pays, licenciee exclusivement par X/Open Company, Ltd.

Sun, Sun Microsystems, le logo Sun, Java, AnswerBook2, docs.sun.com, et Solaris sont des marques de fabrique ou des marques deposees de Sun Microsystems, Inc. aux Etats-Unis et dans d'autres pays.

Toutes les marques SPARC sont utilisees sous licence et sont des marques de fabrique ou des marques deposees de SPARC International, Inc. aux Etats-Unis et dans d'autres pays. Les produits portant les marques SPARC sont bases sur une architecture developpee par Sun Microsystems, Inc.

L'interface utilisateur graphique OPEN LOOK et Sun? a eté developpée par Sun Microsystems, Inc. pour ses utilisateurs et licencies. Sun reconnait les efforts de pionniers de Xerox dans la recherche et le developpement du concept des interfaces utilisateur visuelles ou graphiques pour l'industrie informatique. Sun detient une license non exclusive de Xerox sur l'interface utilisateur graphique Xerox, cette licence couvrant egalement les licencies de Sun implementant les interfaces utilisateur graphiques OPEN LOOK et se conforment en outre aux licences ecrites de Sun.

LA DOCUMENTATION EST FOURNIE "EN L'ETAT" ET TOUTES AUTRES CONDITIONS, DECLARATIONS ET GARANTIES EXPRESSES OU TACITES SONT FORMELLEMENT EXCLUES DANS LA LIMITE DE LA LOI APPLICABLE, Y COMPRIS NOTAMMENT TOUTE GARANTIE IMPLICITE RELATIVE A LA QUALITE MARCHANDE, A L'APTITUDE A UNE UTILISATION PARTICULIERE OU A L'ABSENCE DE CONTREFACON.

# **Table of Contents**

| 1 Introduction5                       |

|---------------------------------------|

| 1.1 Related specifications5           |

| 2 Hypervisor call conventions         |

| 2.1 Hyper-fast traps                  |

| 2.2 Fast traps                        |

| 2.3 Post hypervisor trap processing   |

| 3 State definitions                   |

| 3.1 Guest states                      |

| 3.2 Initial guest environment         |

| 3.3 Privileged registers              |

| 3.4 Other initial guest state10       |

| 4 Addressing Models11                 |

| 4.1 Background11                      |

| 4.2 Address types11                   |

| 4.3 Address spaces11                  |

| 4.4 Address space identifiers11       |

| 4.5 Translation mappings13            |

| 4.6 MMU Demap support13               |

| 4.7 MMU traps                         |

| 4.8 MMU fault status area14           |

| 5 Trap model15                        |

| 5.1 Privilege mode trap processing15  |

| 5.2 Trap levels15                     |

| 5.3 Sun4v privilege mode trap table15 |

| 6 Interrupt model                     |

| 6.1 Definitions16                     |

| 6.2 Interrupt reports                 |

| 6.3 Interrupt queues16                |

| 6.4 Interrupt traps17                 |

| 7 Error model                         |

| 7.1 Definitions                       |

| 7.2 Error classes                     |

| 7.3 Error reports                     |

| 7.4 Error queues 19                   |

| 7.5 Error traps                                     | 19   |

|-----------------------------------------------------|------|

| 8 Machine description                               |      |

| 8.1 Requirements                                    |      |

| 8.2 Sections                                        |      |

| 8.3 Encoding                                        |      |

| 8.4 Header                                          |      |

| 8.5 Name Block                                      |      |

| 8.6 Data Block                                      |      |

| 8.7 Node Block                                      |      |

| 8.8 Nodes                                           |      |

| 8.9 Node definitions                                | 26   |

| 8.10 Content versions                               | 26   |

| 8.11 Summary of node definitions                    | 27   |

| 8.12 Common data definitions                        | 27   |

| 8.13 Generic nodes                                  | 28   |

| 8.14 Memory hierarchy nodes                         | 35   |

| 9 API versioning                                    | 38   |

| 9.1 API call                                        | 38   |

| 10 Domain services                                  | 41   |

| 10.1 API call                                       | 41   |

| 11 CPU services                                     | 47   |

| 11.1 CPU id and CPU list                            | 47   |

| 11.2 API calls                                      | 47   |

| 12 MMU services                                     | 52   |

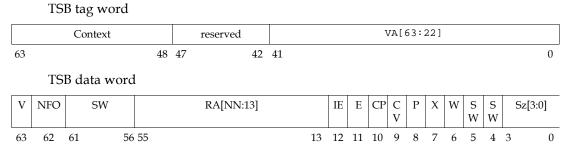

| 12.1 Translation Storage Buffer (TSB) specificati   | on52 |

| 12.2 MMU flags                                      | 54   |

| 12.3 Translation table entries                      | 54   |

| 12.4 Translation storage buffer (TSB) configuration | on56 |

| 12.5 Permanent and non-permanent mappings           | 56   |

| 12.6 MMU Fault status area                          | 56   |

| 12.7 API calls                                      | 60   |

| 13 Cache and Memory services                        | 68   |

| 13.1 API calls                                      | 68   |

| 14 Device interrupt services                        | 70   |

# A Revision 1.0 January 24, 2006

| 14.1 Definitions                         | 70  |

|------------------------------------------|-----|

| 14.2 API calls                           | 70  |

| 15 Time of day services                  | 74  |

| 15.1 API calls                           | 74  |

| 16 Console services                      | 75  |

| 16.1 API calls                           | 75  |

| 17 Core dump services                    | 76  |

| 17.1 API calls                           | 77  |

| 18 Trap trace services                   | 78  |

| 18.1 Trap trace buffer control structure | 78  |

| 18.2 Trap trace buffer entry format      |     |

| 18.3 API calls                           | 79  |

| 19 Logical Domain Channel services       |     |

| 19.1 Endpoints                           |     |

| 19.2 LDC queues                          |     |

| 19.3 LDC interrupts                      |     |

| 19.4 API calls                           |     |

| 20 PCI I/O Services                      | 90  |

| 20.1 Introduction                        |     |

| 20.2 IO Data Definitions                 | 90  |

| 20.3 PCI IO Data Definitions             | 90  |

| 20.4 API calls                           | 93  |

| 21 MSI Services                          | 101 |

| 21.1 Message Signaled Interrupt (MSI)    | 101 |

| 21.2 MSI Event Queue (MSI EQ)            | 101 |

|                                          |     |

|    | 21.3 Definitions                                          | .103  |

|----|-----------------------------------------------------------|-------|

|    | 21.4 API calls                                            | .105  |

| 22 | UltraSPARC T1 performance counters                        | . 112 |

|    | 22.1 Introduction                                         | 112   |

|    | 22.2 Definitions                                          | .112  |

|    | 22.3 API calls                                            | .112  |

| 23 | Niagara-1 MMU statistics counters                         | .114  |

|    | 23.1 Introduction                                         | 114   |

|    | 23.2 Hypervisor API for Niagara MMU statistics collection | .114  |

|    | 23.3 API calls                                            | .116  |

| 24 | Appendix A: How to use a machine description              | .117  |

|    | 24.1 Using the MD as a list                               | .117  |

|    | 24.2 Accelerating string lookups                          | 118   |

|    | 24.3 Directed Acyclic Graph                               | .118  |

|    | 24.4 DAG construction                                     | .119  |

|    | 24.5 Required nodes                                       | 120   |

|    | 24.6 The vanilla MD                                       | . 120 |

|    | 24.7 Formation and meaning of a DAG                       | .120  |

| 25 | Appendix B: Number Registry                               | 122   |

|    | 25.1 Hyper-fast Trap numbers                              | . 122 |

|    | 25.2 FAST_TRAP Function numbers                           | .122  |

|    | 25.3 CORE_TRAP Function numbers                           | .122  |

|    | 25.4 Summary of API service trap and function numbers     | .122  |

|    | 25.5 Error codes                                          | 125   |

|    |                                                           |       |

# 1 Introduction

Sun's UltraSPARC T1 processor has been designed to incorporate hypervisor technology in order to present a virtualized machine environment to any guest operating system running upon it. The resulting software model for a guest operating system is referred to as the "sun4v" architecture. This virtual machine environment is implemented with a thin layer of firmware software (the "UltraSPARC Hypervisor") coupled with hardware extensions providing protection. The UltraSPARC Hypervisor not only provides system services required by the operating system, but it also enables the separation of platform resources into self-contained partitions (logical domains) each capable of supporting an independent operating system image.

This document details the virtual machine environment and the calling conventions of the APIs provided to a sun4v domain by the underlying UltraSPARC hypervisor. The intended audience for this document is operating system and firmware engineers porting to the sun4v architecture.

The API serves two principal purposes:

- 1. To enable the supervisor to request services and operations to be performed on its behalf by the hypervisor.

- 2. To inform the hypervisor of information it expects from the supervisor, for example the size and location of the interrupt delivery queues.

#### 1.1 Related specifications

The sun4v architecture provides a virtual machine environment through a conjunction of platform hardware and hypervisor software. This virtual machine environment consists of a combination of machine registers described by a programmer's reference manual, and a set of software services provided via the hypervisor APIs described in this document.

The hardware registers available within a virtual machine environment, (described in the UltraSPARC Architecture 2005 manual), form the basis of the sun4v hardware architecture. This architecture incorporates the Level-1 SPARC v9 specification. However, it supersedes and extends the Level-2 SPARC v9 specification in describing the programming model, register and exception interfaces for privileged mode software.

In addition to the UltraSPARC Architecture 2005 manual, processor specific details for the UltraSPARC T1 processor are provided in the "UltraSPARC T1<sup>TM</sup> Supplement" manual.

At the time of writing the latest versions of this specification, the UltraSPARC Architecture 2005 manual and the UltraSPARC T1<sup>TM</sup> Supplement are available from the OpenSPARC website (http://www.opensparc.org). The reader is recommended to visit the OpenSPARC website on a regular basis for the most recent versions of these specifications.

The names "Niagara" and "Niagara-1" refer to the UltraSPARC T1 processor.

# 2 Hypervisor call conventions

Hypervisor API calls are made through the use of a trap (Tcc) instruction using  $sw\_trap\_numbers$  0x80 and above. The calling convention has two forms; fast-trap and hyperfast-trap. The principle difference between these two forms is whether the function number is passed in a register or is encoded in the trap instruction itself. The latter is the faster form, but has a limited number of possible functions, and is therefore reserved for performance critical operations only.

# 2.1 Hyper-fast traps

This trap mechanism encodes the API function number (0x80 + a 7bit value) in the Tcc instruction's *sw\_trap\_number* itself, and therefore provides the fastest possible method of reaching the actual function implementation. The calling convention is as follows:

| Register | Input      | Output        |

|----------|------------|---------------|

| %00      | argument 0 | return status |

| %01      | argument 1 | return value1 |

| %02      | argument 2 | return value2 |

| %03      | argument 3 | return value3 |

| %04      | argument 4 | return value4 |

All arguments and return values are 64-bits unless explicitly stated by the description of a specific API service. Further arguments may be passed in memory, as defined on a per function basis.

#### 2.2 Fast traps

Fast traps are the preferred mechanism for hypervisor API calls. Fast trap API calls primarily use *sw\_trap\_number* 0x80 in the Tcc instruction, with the required function number provided as a 64bit value in register %05. The calling convention is as follows:

| Register | Input           | Output         |

|----------|-----------------|----------------|

| %05      | function number | undefined      |

| %00      | argument 0      | return status  |

| %01      | argument 1      | return value 1 |

| %02      | argument 2      | return value 2 |

| %03      | argument 3      | return value 3 |

| %04      | argument 4      | return value 4 |

All arguments and return values are 64-bits **unless** explicitly stated by the description of a specific API service. Further arguments may be passed in memory, as defined on a per function call basis.

#### 2.3 Post hypervisor trap processing

The following convention is used, unless explicitly described for a particular API service:

- All API services resume executing at the next logical instruction after the service trap as with a *done* instruction.

- All sun4v defined registers are preserved across an API service except as explicitly stated below;

- Registers providing arguments to an API service (including the function number %05 for fast traps) should be considered volatile, and their values upon return are undefined unless they are explicitly specified on a per-service basis. Registers not used for passing arguments or returning values are preserved across the API service.

- Upon return from the API service, the returned status is given in register %00. A value of zero in %00 indicates successful execution of the API service, all other values indicate an error status (as defined in section 25.5).

- If an invalid *sw\_trap\_number* is issued, or if an invalid function number is specified, the hypervisor will return with EBADTRAP (as defined in section 25.5) in %00.

- All 64 bits of the argument or return values are significant.

# 3 State definitions

#### 3.1 Guest states

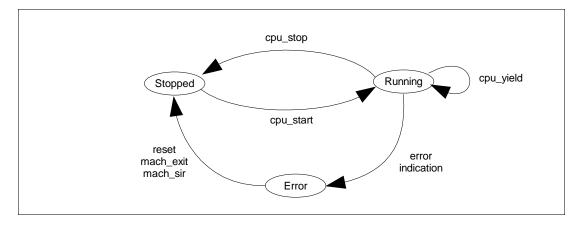

Each virtual CPU can have one of three different states:

| Stopped                                             | CPU is stopped, not executing code, and may be started via the cpu_start API service |

|-----------------------------------------------------|--------------------------------------------------------------------------------------|

| Running                                             | CPU is executing                                                                     |

| Error CPU is in error, and no longer executing code |                                                                                      |

The relationship of these CPU states and hypervisor services may be summarized with the state diagram below:

# 3.2 Initial guest environment

The initial state of each sun4v virtual CPU is defined in the Sun4v Architecture Specification. Initial register state is duplicated here together with initial register configuration performed by the hypervisor for completeness.

#### 3.3 Privileged registers

| Register(s) | Initial Value                             |

|-------------|-------------------------------------------|

| %cwp        | 0                                         |

| %cansave    | NWIN-2                                    |

| %cleanwin   | NWIN-2                                    |

| %canrestore | 0                                         |

| %otherwin   | 0                                         |

| %wstate     | 0                                         |

| %pstate     | all 0 except pstate.priv=1, pstate.mm=tso |

| % tl        | MAXPTL (2)                                |

| %gl         | MAXPGL (2)                                |

| %pil        | MAXPIL (0xf)                              |

| %tba        | current rtba                              |

| %tt         | POR                                       |

# 3.3.1 Non-Privileged Registers

| Register(s)                | Initial Value                          |

|----------------------------|----------------------------------------|

| %g1-%g7                    | 0                                      |

| %i0[%cwp]                  | real address of startup memory segment |

| %i1[%cwp]                  | size of startup memory segment         |

| %i2-%i7[%cwp]              | 0                                      |

| %i0-%i7[all other windows] | 0                                      |

| %10-%17[all windows]       | 0                                      |

| %d0-%d62                   | Binary 0                               |

| %fsr                       | 0                                      |

# 3.3.2 Ancillary State Registers

| Register(s)         | Initial Value                         |

|---------------------|---------------------------------------|

| asr0 (%y)           | 0                                     |

| asr2 (%ccr)         | 0                                     |

| asr3 (%asi)         | ASI_REAL                              |

| asr4 (%tick)        | >0, npt=0                             |

| asr5 (%pc)          | current pc                            |

| asr6 (%fprs)        | 0                                     |

| asr19 (%gsr)        | 0                                     |

| asr22 (%softint)    | 0                                     |

| asr24 (%stick)      | >0, npt=0                             |

| asr25 (%stick_cmpr) | 0 with interrupts disabled (bit 63=1) |

# 3.3.3 Internal memory-mapped registers

| Register(s)                                   | Initial Value    |

|-----------------------------------------------|------------------|

| ASI_SCRATCHPAD, VA=0x00                       | 0                |

| ASI_SCRATCHPAD, VA=0x08                       | 0                |

| ASI_SCRATCHPAD, VA=0x10                       | 0                |

| ASI_SCRATCHPAD, VA=0x18                       | 0                |

| ASI_SCRATCHPAD, VA=0x20                       | 0 if implemented |

| ASI_SCRATCHPAD, VA=0x28                       | 0 if implemented |

| ASI_SCRATCHPAD, VA=0x30                       | 0                |

| ASI_SCRATCHPAD, VA=0x38                       | 0                |

| ASI_MMU, VA=0x08 (primary ctx)                | 0                |

| ASI_MMU, VA=0x10 (secondary ctx)              | 0                |

| ASI_MMU, VA= $0xn08$ (for valid {n} > 0)      | 0                |

| ASI_MMU, VA= $0xn10$ (for valid $\{n\} > 0$ ) | 0                |

| ASI_QUEUE, VA=0x3c0 (cpu mondo head)          | 0                |

| ASI_QUEUE, VA=0x3c8 (cpu mondo tail)          | 0                |

| ASI_QUEUE, VA=0x3d0 (dev mondo head)          | 0                |

| Register(s)                            | Initial Value |

|----------------------------------------|---------------|

| ASI_QUEUE, VA=0x3d8 (dev mondo tail)   | 0             |

| ASI_QUEUE, VA=0x3e0 (res. error head)  | 0             |

| ASI_QUEUE, VA=0x3e8 (res. error tail)  | 0             |

| ASI_QUEUE, VA=0x3f0 (nres. error head) | 0             |

| ASI_QUEUE, VA=0x3f8 (nres. error tail) | 0             |

# 3.3.4 CPU-specific Registers

Platform specific performance counters will be configured such that exceptions/interrupts are disabled.

# 3.4 Other initial guest state

MMU state is disabled.

MMU fault status area location is undefined.

TSB info is undefined.

All queue base addresses and sizes are undefined.

One CPU is placed into the running state, all other CPUs are in the stopped state.

Initial guest soft state is set to SS\_TRANSITION, with an empty (NUL) description string.

# 4 Addressing Models

# 4.1 Background

This section defines the sun4v memory management architecture. The intent is to provide a memory addressing capability for a virtualized architecture at the same time removing the explicit dependence on hardware mechanisms for virtual memory management. Mechanisms are provided to privileged mode to manipulate the memory made available, and in turn to virtualize and make that memory available to non-privileged mode processes.

# 4.2 Address types

The sun4v architecture has two address types, as in legacy architectures. The main difference is that *virtual adresses* are translated to *real addresses*, as opposed to being translated to *physical addresses*. This change is made in order to enable the segregation of physical memory into multiple partitions.

- *Virtual addresses* are translated by an MMU in order to locate data in physical memory. This definition is unchanged from current systems for nonprivileged and privileged mode addresses.

- *Real addresses* are provided to privileged mode code to describe the underlying physical memory allocated to it. Translation storage buffers (TSBs) maintained by privileged mode code are used to translate privileged or nonprivileged mode virtual addresses into real addresses. MMU bypass addresses in privileged mode are also real addresses.

# 4.3 Address spaces

Address spaces are unchanged from UltraSPARC-1. Primary and secondary virtual addresses are associated with context identifiers that are used by privileged code to create multiple address spaces.

# 4.4 Address space identifiers

Instructions can explicitly specify an address space via address space identifiers. All the SPARC v9 ASI definitions are unchanged for sun4v, and a number of new ASIs are also defined. ASIs related to memory management are described below:

| ASI # | ASI Name        |

|-------|-----------------|

| 0x14  | REAL_MEM        |

| 0x15  | REAL_IO         |

| 0x1c  | REAL_MEM_LITTLE |

| 0x1d  | REAL_IO_LITTLE  |

| 0x21  | MMU             |

# 4.4.1 ASI 0x14 & 0x1c : REAL\_MEM{\_LITTLE}

This ASI provides privileged mode access to cached memory using a real rather than virtual address. For this access the context id is unused. A *nonresumable\_error* trap occurs if the access cannot be completed.

# 4.4.2 ASI 0x15 & 0x1d : REAL\_IO{\_LITTLE}

This ASI provides privileged mode access to uncached memory addresses using a real rather than virtual address. For this access the context id is unused. A *nonresumable\_error* trap occurs if the access cannot be completed.

### 4.4.3 ASI 0x26 & 0x2E : REAL\_QUAD{\_LITTLE}

This ASI provides atomic access to 16 bytes of data using real addresses. A *mem\_address\_not\_aligned* trap is taken if the address is not 16 byte aligned.

#### 4.4.4 ASI 0x21 : MMU

The sun4v MMU interface consists of the following registers:

| Register           | Address |

|--------------------|---------|

| PRIMARY_CONTEXTn   | 0xn08   |

| SECONDARY_CONTEXTn | 0xn10   |

These registers are used for the primary and secondary context values utilized by the processor TLB for distinguishing address space contexts. The number of primary and secondary context registers provided is implementation dependent subject to the following rules:

- 1. The number of primary context registers must be the same as the number of secondary context registers.

- 2. The context registers must start with n=0, and be arranged sequentially without gaps. So, for example with 4 registers, n=0,1,2,3.

- 3. The number of bits provided must be the same for all context registers.

- 4. For ease of programming, a write to PRIMARY\_CONTEXT0 causes the same context value to be written to all other PRIMARY\_CONTEXT registers. Similarly, a write to SECONDARY\_CONTEXT0 causes the same context value to be written to all other SECONDARY\_CONTEXT registers.

Sun4v provides a minimum of 13 bits of context (bits 0 through 12). Further bits (from 13 and up) may be provided as an implementation dependent feature. The maximum number of bits for a given hardware platform are given as a property in the guest's machine description. Privileged code is responsible for honoring the number of bits supported by hardware.

#### 4.4.4.1 Programming note

The policy of how privileged code chooses to use the primary and secondary context registers is beyond the scope of this document. However, because sun4v only guarantees the existence of PRIMARY\_CONTEXT0 and SECONDARY\_CONTEXT0 it is recommended that these be used as process private context registers, while any remaining context registers be used for possibly shared context address spaces.

#### 4.4.4.2 Translation conflicts

For sun4v platforms that implement more than one primary and more than one secondary context register privileged code must ensure that no more than one page translation is allowed to match at any time.

An illustration of erroneous behavior is as follows: an operating system constructs a mapping for virtual address A valid for context P, it then constructs a mapping for address A for context Q. By setting PRIMARY\_CONTEXT0 to P and PRIMARY\_CONTEXT1 to Q both mappings would be active simultaneously - potentially with conflicting translations for address A.

Care must be taken not to construct such scenarios.

To prevent errors/data corruption sun4v processors will detect such conflicts, flush the TLB, and issue a {*data/instruction*}\_access\_exception.

#### 4.4.4.3 Barrier rules

By definition changing either the primary or secondary context registers has side effects on processor behavior. The following table describes the behavior of a stxa to these registers.

|                   | @ TL = 0                                                                                                | @ TL > 0                                                                                                                 |

|-------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| PRIMARY_CONTEXT   | undefined; privileged code should not<br>change PRIMARY_CONTEXT at TL=0                                 |                                                                                                                          |

| SECONDARY_CONTEXT | membar #Sync is required for effects<br>to be guaranteed observable,<br>otherwise results are undefined | membar #Sync, DONE or RETRY are<br>required for effects to be guaranteed<br>observable, otherwise results are undefined. |

#### 4.5 Translation mappings

Privileged code describes virtual to real address mappings to manage its virtual address spaces. These mappings are declared either as translation table entries (TTEs) in a translation storage buffer (TSB) described in section 12.1, or can be established directly by the use of the hypervisor API call mmu\_map\_perm\_addr (§12.7.7). This call can also be used to establish a limited number of "locked" mappings for which privileged code cannot tolerate an MMU miss trap.

#### 4.6 MMU Demap support

Privileged mode demap operations become hypervisor API calls.

It is important to note that sun4v provides a coherent demap capability for the privileged mode. The demap API call takes a list of virtual CPUs for which the demap operation is to be applied.

The following three demap operations are required for sun4v:

| Demap Page                                     | The translations demapped match the virtual address and context id designated. |

|------------------------------------------------|--------------------------------------------------------------------------------|

| Demap Context                                  | the translations demapped match the context id designated.                     |

| <i>Demap All</i> this demaps all translations. |                                                                                |

#### 4.7 MMU traps

MMU privilege mode traps are a subset of the MMU traps described in the SPARC v9 specification:

{instruction,data}\_access\_mmu\_miss

shall be generated when a nonprivileged or privileged mode access does not have a translation in any of the TSBs.

#### data\_access\_protection

shall be generated when a nonprivileged or privileged mode access matches a translation that does not allow the requested action, i.e. store when TTE write enable field is clear. This also enables software simulation of a TLB entry *modified* bit, as well as fast *copy-on-write* page processing.

To speed processing of a copy-on-write or modified-bit usage, the faulting TLB entry is guaranteed flushed from the local CPU's TLB upon entry of this exception. Thus, in the common case, no flush operation needs to be generated before enabling write permission in the faulting TTE.

#### *{instruction,data}\_access\_exception*

shall be generated as the result of a nonprivileged mode access when TTE privilege field is set, or as the result of an instruction fetch when the TTE execute permission bit is not set, or as the result of two conflicting translation matches for the same virtual address.

#### *fast\_{instruction,data}\_access\_MMU\_miss*

shall be generated when a nonprivileged or privileged mode access does not have a translation in any TLB and no TSB is specified for the virtual cpu.

#### fast\_data\_access\_protection

shall be generated when no TSB is specified for the virtual cpu and a nonprivileged or privileged mode access matches a TLB translation that does not allow the requested action, i.e. store when TTE write enable field is clear. This also enables software simulation of a TLB entry *modified* bit, as well as fast *copy-on-write* page processing.

To speed processing of a copy-on-write or modified-bit usage, the faulting TLB entry is guaranteed flushed from the local CPU's TLB upon entry of this exception. Thus, in the common case, no flush operation needs to be generated before enabling write permission in the faulting TTE.

#### 4.8 MMU fault status area

MMU related faults have their status and fault address information placed into a memory region made available by privileged code. Like the TSBs above, the fault status area for **each** virtual processor is declared via a hypervisor API call.

The MMU fault area is arranged on an aligned address boundary with instruction and data fault fields arranged into distinct 64byte blocks. The contents and layout of the MMU fault status area are currently specified in section12.6 of this specification.

# 5 Trap model

For sun4v, two of the three SPARC v9 trap types: precise and disrupting, behave according to the SPARC v9 specification. The third, deferred, may behave according to the UltraSPARC-I specification. The key difference is that UltraSPARC-I deferred traps do not provide additional information so that uncompleted instructions older than TPC can be emulated.

In the case of a CPU that implements SPARC v9 deferred traps, the hypervisor will present a deferred trap to privileged mode, but will also make available enough information so that privileged code can attempt to emulate any uncompleted instructions. In the case of a non-resumable error trap, the emulation information will appear in the error report. This is also the rationale for not including the SPARC v9 FQ register in sun4v, since it is used for emulation of deferred floating point traps.

A more precise description of the MMU, interrupt and error traps is made below to clarify behaviors left unspecified by SPARC v9.

#### 5.1 Privilege mode trap processing

As with the SPARC v9 specification, the processor's action during trap processing depends on the trap type, the current trap level (TL register), and the processor state.

For trap processing from non-privileged or privileged mode to privileged mode the steps taken are the same as the SPARC v9 specification. Note that if a privileged code lowers the value of TL, there is no guarantee that the values of TSTATE, TPC, TNPC and TT will remain consistent for larger values of TL.

#### 5.2 Trap levels

The maximum trap level available to privileged software in sun4v is defined to be 2 (MAXPTL).

# 5.2.1 Privilege mode TL overflow

When TL = MAXPTL, an additional privileged mode trap results in the delivery of a *watchdog\_reset* trap to privileged mode with TT set to the type of trap that caused the error. TL remains at MAXPTL.

# 5.3 Sun4v privilege mode trap table

The privileged mode trap table is defined in the programmers reference manual for each specific processor.

# 6 Interrupt model

This chapter describes the sun4v architecture for sending and receiving interrupts.

# 6.1 Definitions

| CPU mondo        | CPU to CPU interrupt message.     |

|------------------|-----------------------------------|

| Device mondo     | interrupt sent by an I/O device.  |

| Interrupt report | a message describing an interrupt |

| Interrupt queue  | a FIFO list of interrupt reports  |

#### 6.2 Interrupt reports

Interrupts are described by interrupt reports. Each interrupt report is 64 bytes long and consists of eight 64-bit words. If a report contains less than eight meaningful words it will be padded with zeros.

#### 6.3 Interrupt queues

Interrupts are indicated to privileged mode via interrupt queues each with its own associated trap vector. There are 2 interrupt queues, one for device mondos and one other for CPU mondos. New interrupts are appended to the tail of a queue, and privileged code reads them from the head of the queue.

Privileged code is responsible for allocating real memory regions for these queues. Each queue region must be a power of 2 multiple of 64 bytes in size. The base real address must be aligned to the size of the region. For example, a queue of 128 entries is 8K bytes in size and must be aligned on an 8K byte real memory address boundary.

The queue configuration is described via hypervisor API calls when the queue region is created or modified (see section 11.2.6).

# 6.3.1 Queue support registers

The contents of each queue is described by a head and tail pointer. The head and tail pointer for each queue are held in registers as offsets from the base of their respective queue region. These interrupt queue registers are accessed with the QUEUE ASI (0x25). Each of the registers are addressable and accessible as 64bit quantities. The ASI addresses are as follows:

| Register             | Address | Access |

|----------------------|---------|--------|

| CPU_MONDO_QUEUE_HEAD | 0c3c0   | rw     |

| CPU_MONDO_QUEUE_TAIL | 0x3c8   | ro     |

| DEV_MONDO_QUEUE_HEAD | 0x3d0   | rw     |

| DEV_MONDO_QUEUE_TAIL | 0x3d8   | ro     |

In privileged mode, the head offset registers are read and write accessible, the tail offset registers are only readable. Attempting to write the tail register from privileged mode results in a *data\_access\_exception* trap.

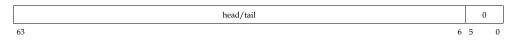

# 6.3.1.1 \*\_QUEUE\_HEAD and \*\_QUEUE\_TAIL

The status of each queue is reflected by its head and tail pointers:

\*\_QUEUE\_HEAD holds the offset to the oldest interrupt report in the queue.

\*\_QUEUE\_TAIL holds the offset to the area where the next interrupt report will be stored.

An event that results in the insertion of a queue entry causes the tail of that queue to be incremented by 64 bytes. Privileged code is responsible for similarly incrementing the head pointer to remove an entry from the queue. The queue pointers are updated using modulo arithmetic based on the size of a queue. A queue is empty when the head is equal to the tail. A queue is full when the insertion of one more entry would cause the tail pointer to equal the head pointer.

| head/tail |   | 0 |   |

|-----------|---|---|---|

| 63 6      | 5 | j | 0 |

Figure 1 : Head and Tail register formats

The format of each of the QUEUE\_HEAD and QUEUE\_TAIL register is shown in Figure 1. Bits 0 through 5 always read as 0, and attempts to write them are ignored.

The minimum head and tail register size is provided as a property value in the machine description given to a guest.

#### 6.4 Interrupt traps

The sun4v architecture has an interrupt trap for each of the two interrupt queues:

cpu\_mondothis trap informs privileged mode that an interrupt report has been<br/>appended to the CPU mondo queue.dev\_mondothis trap informs privileged mode that an interrupt report has been<br/>appended to the dev mondo queue.

Both traps are disrupting, meaning that the current instruction stream can be restarted with a retry instruction, and that they can be blocked by setting pstate.ie = 0.

#### 6.4.1 CPU mondo interrupts

CPU to CPU messages are are sent via CPU mondo interrupts. The term mondo refers to the original UltraSPARC-1 bus transaction where they were first introduced.

#### 6.4.1.1 Sending CPU mondos

CPU mondos are sent via hypervisor API calls. The API allows 64 bytes of data to be sent to the targeted CPUs. The API call also includes the ability to send mondos to multiple CPUs in a single call to improve efficiency.

#### 6.4.1.2 Receiving CPU mondos

CPU mondos are received via the CPU mondo queue.. When this queue is non-empty, a *cpu\_mondo* disrupting trap is pended to the target CPU. The mondo data received is stored as the interrupt report.

#### 6.4.2 Device mondo interrupts

Device mondo interrupts are received via the device mondo queue. When this queue is non-empty, a *dev\_mondo* disrupting trap is pended to the target CPU. The interrupt report contents are device-specific, although a hypervisor API call does exist to allow privileged code to target device interrupts to specific CPUs.

# 7 Error model

This section describes the sun4v error handling and reporting architecture. To allow for a degree of future proofing, this component of sun4v has to be flexible, and robust enough to gracefully cope with error situations yet to be envisioned by system designers. In particular it is a design goal of sun4v that an older sun4v OS be able to handle reports from new hardware - if only via a set of default actions.

# 7.1 Definitions

| Error class  | a group of errors with common attributes that are handled in a similar manner. |

|--------------|--------------------------------------------------------------------------------|

| Error report | a message describing an error sent to privileged mode.                         |

| Error queue  | a FIFO list of error reports of the same class.                                |

# 7.2 Error classes

The sun4v architecture defines two classes of errors: resumable and non-resumable errors.

#### 7.2.1 Resumable error

A resumable error indicates the delivery of an error notification that leaves the current instruction stream in a consistent state so that execution can be resumed after the error is handled. A resumable error does not require any specific action by privileged code; the error may even be ignored. More sophisticated privileged code may record the error and/or forward it to a diagnosis agent. While all corrected errors are resumable, it is important to note that some uncorrectable errors are also resumable, e.g., an uncorrectable writeback error is resumable since the current instruction stream is not affected, but if the corrupted data is later fetched, a nonresumable error would occur. Whether or not the error was corrected is indicated in the error header.

#### 7.2.2 Non-resumable error

A non-resumable error indicates the delivery of an error notification that leaves the current instruction stream in an inconsistent state. The instruction stream (nonprivileged or privileged) interrupted by this error cannot be resumed without explicit software intervention. In addition to possibly recording the error and/or forwarding it to a diagnosis agent, privileged code must either abort the current instruction stream, or attempt to recover from the error. The instruction stream may only be repaired if the error caused a precise trap. If the error caused a deferred trap, it cannot be repaired. The error's trap type is indicated in the error header.

#### 7.3 Error reports

The sun4v architecture presents error information to privileged mode via error reports. An error report consists of a common 64 byte header, followed by error-specific data. The error-specific data will also be a multiple of 64 bytes in length, so the entire length of an error message will always be a multiple of 64 bytes.

#### 7.4 Error queues

Errors are reported to privileged mode via error reports. Error reports are appended to a FIFO error queue. There are two error queues, one for each error class (resumable and non-resumable). Privileged code removes errors from the front of the error queue as it handles them.

The contents of each queue is described by a head and tail pointer. The head and tail pointer for each queue are held in registers as offsets from the base of their respective queue region. These interrupt queue registers are accessed with the QUEUE ASI (0x25). Each of the registers are addressable and accessible as 64bit quantities. The ASI addresses are as follows:

| Register                      | Address | Access         |

|-------------------------------|---------|----------------|

| RESUMABLE_ERROR_QUEUE_HEAD    | 0x3e0   | read & write   |

| RESUMABLE_ERROR_QUEUE_TAIL    | 0x3e8   | read only      |

| NONRESUMABLE_ERROR_QUEUE_HEAD | 0x3f0   | read and write |

| NONRESUMABLE_ERROR_QUEUE_TAIL | 0x3f8   | read only      |

In privileged mode, the head offset registers are read and write accessible, the tail offset registers are only readable. Attempting to write the tail register from privileged mode results in a *data\_access\_exception* trap.

#### 7.4.1 \*\_QUEUE\_HEAD and \*\_QUEUE\_TAIL

The status of each queue is reflected by its head and tail pointers:

- \*\_QUEUE\_HEAD holds the offset to the oldest error report in the queue.

- \*\_QUEUE\_TAIL holds the offset to the area where the next error report will be stored.

An event that results in the insertion of a queue entry causes the tail of that queue to be incremented by 64 bytes. Privileged code is responsible for similarly incrementing the head pointer to remove an entry from the queue. The queue pointers are updated using modulo arithmetic based on the size of a queue. A queue is empty when the head is equal to the tail. A queue is full when the insertion of one more entry would cause the tail pointer to equal the head pointer.

# Figure 2 : Head and Tail register formats

The format of each of the QUEUE\_HEAD and QUEUE\_TAIL register is shown in Figure . Bits 0 through 5 always read as 0, and attempts to write them are ignored.

The minimum head and tail register size is 16 bits (bits 6 though 21). Unimplemented bits must read as zero, and be ignored when written.

#### 7.5 Error traps

The sun4v architecture has two error traps:

*resumable\_error* this trap informs privileged code that an error report has been appended to the resumable error queue. This trap is a disrupting trap, meaning that the current instruction stream can be restarted with a retry instruction, and that *resumable\_error* traps can be blocked by setting pstate.ie = 0.

*nonresumable\_error* this trap informs privileged code that an error report has been appended to the nonresumable error queue. This trap may be precise or deferred, as indicated in the error header. A precise trap may be restartable if the corruption can be repaired, but a deferred trap cannot be restarted even if the corruption is repaired. Non-resumable errors cannot be blocked, or nest. Privileged code must update the nonresumable queue head as quickly as possible to indicate when it is prepared to take another *nonresumable\_error* trap. If the nonresumable\_error queue is not empty when another *nonresumable\_error* trap occurs, the hypervisor will stop the current CPU, and send a resumable error to another CPU in the same partition. If only one CPU has been configured in the partition, the hypervisor will inform the service processor.

At entry of the trap handler, the processor caches will be enabled and cleared of any faults. System memory, however, may have uncorrectable errors. If the real address of a memory error can be determined, this information will appear in the error header.

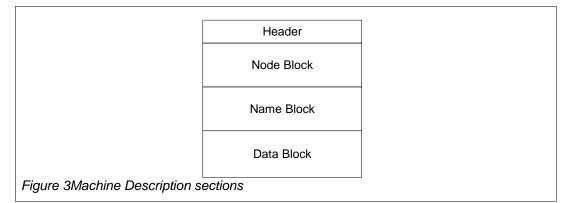

# 8 Machine description

To describe the resources within a virtual machine (or logical domain), a data structure called a machine description (MD) is made available to the guest running in each logical domain / virtual machine environment.

This section describes the transport format for the machine description (MD).

This format is provided for the contract between the producer of the MD (typically the Service Entity) and the consumers in the logical domains (for example, OBP boot firmware and the Solaris OS.)

#### 8.1 Requirements

The format of the machine description is designed so that any consumer may either elect to read and transform it into an internal representation, or merely use it in place. For the latter, the encoding needs to be easily readable with an efficient decoder. Similarly a simple encoding requirement also exists for the system software responsible for generating a particular machine description.

A hypervisor will provide a machine description as a whole to a guest operating system upon request in response to an API call. The machine description is written into a buffer owned by the guest, and not shared with any other guest or with the hypervisor. Once provided it is truly private to the guest. Therefore, there is no requirement that the encoding format support any form of dynamic update or extension. Updates to a machine description are indicated by providing a complete new machine description.

#### 8.2 Sections

The machine description is provided in four sections as illustrated below and described below.

These sections are linearly concatenated together to provide a single machine description.

# 8.3 Encoding

Unless otherwise specified, all fields described herein are encoded in network byte order (big-endian).

Unless otherwise specified, all fields are packed without intervening padding, and have no required byte alignment.

Where alignment is specified, it is defined in relation to the first byte of the machine description header.

#### 8.4 Header

The format for the machine description header is defined below:

| Byte offset | Size in bytes | Field name        | Description                 |

|-------------|---------------|-------------------|-----------------------------|

| 0           | 4             | transport_version | Transport version number    |

| 4           | 4             | node_blk_sz       | Size in bytes of node block |

| 8           | 4             | name_blk_sz       | Size in bytes of name block |

| 12          | 4             | data_blk_sz       | Size in bytes of data block |

The header is easily described by the following packed C structure for a big-endian machine:

| struct MD_HEADER | {                             |

|------------------|-------------------------------|

| uint32_t         | <pre>transport_version;</pre> |

| uint32_t         | node_blk_sz;                  |

| uint32_t         | name_blk_sz;                  |

| uint32_t         | data_blk_sz;                  |

| };               |                               |

The transport\_version specifies the version encoding that applies to this MD. The transport version is a 32bit integer value. The upper 16bits correspond to a major version number, the lower 16bits correspond to a minor version number change.

#### 8.4.1 Version numbering

The transport\_version number for this specification is 0x10000, namely version 1.0.

An increase in the minor number of the transport version corresponds to the compatible addition or removal of information encoded in the machine description. This includes, but is not limited to, the removal of certain property types, or the addition of new property types. Guests can expect to be able to decode some, but not all of the Machine Description, and must handle this expectation accordingly by ignoring unknown types.

Future specification revisions defining new element types found outside a node encapsulation (e.g. between NODE\_END and NODE) are considered incompatible and require an increase in the major version number of the MD transport header.

## 8.4.2 Size fields

- Each size field describes the size in bytes of the remaining three blocks in the machine description.

- The node block follows immediately after the section header.

- The name block starts at byte offset: 16+ node\_blk\_sz.

- The data block starts at byte offset: 16 + node\_blk\_sz + name\_blk\_sz.

- All sizes are multiples of 16 bytes.

- The total size of the MD is 16 + node\_blk\_sz + name\_blk\_sz + data\_blk\_sz.

- Each section (sizes; node\_blk\_sz, name\_blk\_sz, data\_blk\_sz) may be a maximum of 2<sup>32</sup>-16 bytes in length.

Note: The name block and data block sections are described below first, to assist in understanding of the subsequent node block description.

#### 8.5 Name Block

The name block provides name strings to be used for node entry naming. Legal name strings are defined as follows:

A name string is a human readable string comprised of an unaligned linear array of bytes (characters) terminated by a zero byte (nul '\0' character). Null termination enables the use of C functions such as strcmp(3) for comparison.

Character encoding consists of all human readable letters and symbols from ISO standard 8859-1 not including: blanks, "/", "\", ";", "[", "]", "@".

Each name string is referenced by its starting byte offset within the name block.

Name string lengths are stored along with the byte offset in the node elements, limiting name length to 255 bytes, not including the terminating null character.

There may not be duplicate strings in the name block; a given name string may appear only once in the name block. Thus the offset within the name block becomes a unique identifier for a given name string within a machine description.

A single name string may be referenced from more than one node element.

The name block is padded with zero bytes to ensure that the subsequent data block is aligned on a 16 byte boundary relative to the start of the machine description. These pad bytes are included in the name block size.

Note: The name block contains name strings that are held independently from the data block section in order to assist with accelerated string lookups. This technique is described later in section 24.2.

#### 8.6 Data Block

The data block provides raw data that may be referenced by nodes in the node block.

Raw data associated with node block elements is simply a linear concatenation of the raw data itself and has no further intrinsic structure. The size, location and content of each data element is identified by the referring element in the node block.

Data block contents are unaligned unless specified as part of the referring property's requirements. When alignment is required it is considered relative to the first byte of the overall machine description. Alignment is achieved by preceeding a data element with zero bytes in the data block.

The producer of a machine description is required to arrange that data requiring a specific alignment in the MD is placed on an appropriate alignment boundary relative to the start of the MD. The consumer of an MD is required to read the machine description into a buffer aligned correctly for the largest alignment requirement the consumer may have, or be prepared to handle unaligned data references correctly.

#### 8.7 Node Block

The node block is comprised of a linear array of 16 byte elements aligned on a 16byte boundary relative to the first byte of the entire machine description.

The node block elements have specific types and are grouped as defined below so as to form "nodes" of data. Each element is of fixed length, and each element may be uniquely identified by its index within the node block array.

Any element A may refer to another element B simply by using the array index for the location of element B. For example, the first element of the node block has index value 0, the second has index 1, and so on.

#### 8.7.1 Element format

Elements within the node block have a fixed 16byte length format comprised of bigendian fields described below:

| Byte offset | Size in bytes | Field name      | Description                                                                                                                                    |

|-------------|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 0           | 1             | tag             | Type of element                                                                                                                                |

| 1           | 1             | name_len        | Length in bytes of element name. Element name is located in the name block.                                                                    |

| 2           | 2             | _reserved_field | reserved field (contains bytes of value 0)                                                                                                     |

| 4           | 4             | name_offset     | Location offset of name associated with this element relative to start of name block.                                                          |

| 8           | 8             | val             | 64 bit value for elements of tag type "NODE",<br>"PROP_VAL" or "PROP_ARC"                                                                      |

| 8           | 4             | data_len        | Length in bytes of data in data block for elements of type "PROP_STR" and of type "PROP_DATA"                                                  |

| 12          | 4             | data_offset     | Location offset of data associated with this element<br>relative to start of data block for elements of tag type<br>"PROP_STR" and "PROP_DATA" |

For a big-endian machine this is illustrated by the packed C structure below:

```

struct MD_ELEMENT {

uint8_t

tag;

uint8_t

name_len;

_reserved_field;

uint16_t

uint32_t

name_offset;

union {

struct {

uint32_t

data_len;

uint32_t

data_offset;

} y;

uint64_t

val;

} d;

```

The tag field defines how each element should be interpreted.

The name associated with this element is given by the name\_offset and name\_len fields giving the offset within the name block and length of the node name not including the terminating null character.

The remainder of the node element has two formats depending upon the node tag field. The node element either contains a 64bit immediate data value, or (for elements requiring an extended data or string) it consists of two 32bit values providing the size and offset of the relevant data within the data block.

};

# 8.7.2 Tag definitions

Note: Element tag enumerations are chosen so that an ASCII dump of the node section will reveal each element type thus aiding debugging.

| Tag Value | ASCII equiv                 | Name      | Description                           | Value field                                                     |

|-----------|-----------------------------|-----------|---------------------------------------|-----------------------------------------------------------------|

| 0x0       | \0                          | LIST_END  | End of element list                   | -                                                               |

| 0x4e      | 'N'                         | NODE      | Start of node definition              | 64bit index to next node<br>in list of nodes                    |

| 0x45      | 'E'                         | NODE_END  | End of node definition                | -                                                               |

| 0x20      | 11                          | NOOP      | NOOP list element - to be ignored     | 0                                                               |

| 0x61      | 'a'                         | PROP_ARC  | Node property arc'ing to another node | 64bit index of node<br>referenced                               |

| 0x76      | <sup>1</sup> V <sup>1</sup> | PROP_VAL  | Node property with an integer value   | 64bit integer value for property                                |

| 0x73      | 's'                         | PROP_STR  | Node property with a string value     | offset and length of<br>string within data block                |

| 0x64      | 'd'                         | PROP_DATA | Node property with a block of data    | offset and length of<br>property data with in the<br>data block |

The following element tag types are defined:

#### 8.8 Nodes

The array of elements in the node block form a sequence of "nodes" terminated by a single LIST\_END element.

- A node is a linear sequence of two or more elements whose first element is NODE and whose last element is NODE\_END.

- Between NODE and NODE\_END there are zero or more elements that define properties for that node. These are PROP\_\* elements. The ordering of these elements (between NODE and NODE\_END) does not confer meaning.

- The name given to a NODE element is non-unique and defines the binding of property elements that may be encapsulated within that node.

- The NOOP element is provided so that an entire node may be removed by overwriting all of its constituent elements with NOOP. A NODE link that arrives at a NOOP element is equivalent to the next NODE or LIST\_END element after the sequence of NOOP elements.

- The PROP\_ARC element is used to denote an arc in a DAG, therefore a PROP\_ARC element may only reference a NODE element.

- Note: A node referenced by any PROP\_ARC element cannot be removed by use of NOOP element unless all the referring PROP\_ARC elements are removed. PROP\_ARC elements may be removed by conversion to a NOOP element.

- The element index of a "NODE" element is serves as a unique identification of a complete node and its encapsulated properties.

- The value field associated with a "NODE" element (elem\_ptr->d.val) holds the element index to the next "NODE" element within the MD.

A reader may skip from one node to the next without having to scan within each node for the "NODE\_END" by using this index value to locate the next NODE element in the node block.

#### 8.9 Node definitions

The type of a node is defined by the name string associated with the NODE element designating the start of the node in the machine description node block. Nodes can be found by linear search matching on type or by following the PROP\_ARCs of a DAG.

#### 8.9.1 Node categories

Nodes in a machine description serve one or two purposes; to provide information about a virtual machine resource they represent and, optionally to function as a construction node within a DAG formed within the machine description. A construction node may contain properties about certain resources, however its primary function is as a container for the arc links (PROP\_ARC properties) that connect to other descriptive nodes.

Nodes belong to one of four categories that determine what walkers must handle within the MD. A node's category determines whether nodes of that type can be expected to found within the MD, or whether nodes of that type are optional. The categories are defined below:

| core              | Nodes of this type are always required to be present in the MD.                                                                                                                       |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| resource required | If the resource described by the node is available within the virtual machine, an associated node of this type is required to be present in the MD in order to describe the resource. |

| required by X     | If a node of type X is present in the MD, then one (or more) nodes of this type will be present in the MD and associated with X.                                                      |

| optional          | A node of this type need not appear as part of the MD, it is entirely optional, and guest OS code should have a default policy to continue functioning despite this absence.          |

#### 8.10 Content versions

The "root" node (section 8.13.1) is unique in the entire machine description. It is; the one node from which all other nodes can be reached, guaranteed to be the first node defined in the node block, and is required to be present in a properly formed machine description.

The root node is primarily a construction node, with arc properties connecting to other nodes in the description. The root node carries a string property "content-version" that defines the version number of the content of the machine description".

Content versioning is defined independently of the machine description transport version. The content version identifies the rules surrounding construction of the DAG describing the machine.

This specification is for content version "1".

Minor changes such as the addition of new node types, properties or arc names, or the removal of optional nodes or properties, do not require a content version number change.

Incompatible changes to the node definitions such that any possible earlier machine description consumer will encounter problems with the newer content cause a version change.

# 8.11 Summary of node definitions

| Node Name | Defined in section | Brief description                                        |

|-----------|--------------------|----------------------------------------------------------|

| cache     | 8.14.1             | Definition of a cache in the memory system hierarchy     |

| cpu       | 8.13.3             | Definition node for a single CPU                         |

| cpus      | 8.13.2             | Construction node pointing to all cpu nodes              |

| exec_unit | 8.14.2             | Node describing an execution unit of processor           |

| mblock    | 8.13.5             | Definition of single block of available memory           |

| memory    | 8.13.4             | Construction node pointing to all available mblock nodes |

| platform  | 8.13.6             | Node describing intrinsic platform properties            |

| root      | 8.13.1             | The primary node                                         |

| tlb       | 8.14.3             | Definition of a TLB in the memory system heirarchy       |

The list of currently defined nodes is as follows:

Note: Nodes not defined in this specification must be ignored by system-software.

Each of the above nodes is defined in more detail in the following sections.

# 8.12 Common data definitions

As defined by the machine description transport, data values for string and data property elements (PROP\_STR and PROP\_DATA) are placed in the data block of the machine description. This section defines commonly used formats of data placed in the data block of a machine description and referred to using elements with the PROP\_DATA tag.

Additional data formats may also be defined explicitly with a specific node definition.

#### 8.12.1 String array

A string array is a commonly used data property that defines a concatenated list of nul character terminated strings. The PROP\_DATA element that refers to this structure carries an offset (within the MD data block) to the start of the first string. The size field corresponds to a count of all the string bytes comprising the compound string list.

In this format strings are concatenated one immediately after the next. Thus if p is a pointer to the first string, then p+strlen(p)+1 is a pointer to the second. The overall size of this data field is used to determine the last string in the list. Every string in the list must terminate with the nul character. The string pointed to by p is the last string in the array if p+strlen(p)+1 equals the address of the property data plus its length. A string array of zero elements is not possible since the data length of a PROP\_DATA element cannot be zero. Consumers should interpret the absence of the property as indicating an array of zero elements.

For example; the string list { "data", "load", "store" } would be encoded as a PROP\_DATA pointing to a 16byte block of the data section of the MD with the byte values: 0x64 0x61 0x74 0x61 0x00 0x6c 0x6f 0x61 0x64 0x00 0x73 0x74 0x6f 0x72 0x65 0x00.

# 8.13 Generic nodes

### 8.13.1 Root node

| Name | Category | Required subordinates | Optional subordinate |

|------|----------|-----------------------|----------------------|

| root | core     | cpus (§8.13.2)        |                      |

|      |          | memory (§8.13.4)      |                      |

|      |          | platform (§8.13.6)    |                      |

#### 8.13.1.1 Description

A node of this type must always be the first node in a machine description.

Only one node in the machine description may be named "root".

This root node must be the first node defined in the node block of the machine description.

All other nodes in the forward graph can be reached starting at the root node.

#### 8.13.1.2 Properties

| Name            | Tag      | Required | Description                                                                                     |

|-----------------|----------|----------|-------------------------------------------------------------------------------------------------|

| content-version | PROP_STR | yes      | Version string for the content of this machine description.<br>Currently defined version is "1" |

# 8.13.2 Cpus node

| Name | Category         | Required subordinates | Optional subordinate |

|------|------------------|-----------------------|----------------------|

| cpus | required by root |                       | cpu(§8.13.3)         |

# 8.13.2.1 Description

This construction node leads directly to all the virtual CPUs supported within this virtual machine. The number of cpus is expected to be derived by counting the number of subordinate cpu nodes.

# 8.13.2.2 Properties

None defined

# 8.13.3 Cpu node

| Name | Category | Required subordinates | Optional subordinate |

|------|----------|-----------------------|----------------------|

| сри  | resource |                       | exec_unit (§8.14.2)  |

|      | required |                       | cache (§8.14.1)      |

|      |          |                       | tlb (§8.14.3)        |

# 8.13.3.1 Properties

| Name                 | Tag        | Required | Description                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clock-frequency      | PROP_VAL   | yes      | A 64-bit unsigned integer giving the frequency of the sun4v<br>virtual CPU in Hertz and thereby the frequency of the<br>processor's %tick register                                                                                                                                                                                                                            |

| compatible           | PROP_DATA* | yes      | String array of cpu types this virtual cpu is compatible with.<br>The most specific cpu type must be placed first in the list,<br>finishing with the least specific.                                                                                                                                                                                                          |

| id                   | PROP_VAL   | yes      | A unique 64-bit unsigned integer identifier for the virtual<br>CPU. This identifier is the one to use for all hypervisor CPU<br>services for the CPU represented by this node.                                                                                                                                                                                                |

| isalist              | PROP_DATA* | yes      | List of the instruction set architectures supported by this virtual CPU.                                                                                                                                                                                                                                                                                                      |

| mmu-#context-bits    | PROP_VAL   | no       | A 64-bit unsigned integer giving the number of bits forming<br>a valid context for use in a sun4v TTE and the MMU context<br>registers for this virtual CPU.                                                                                                                                                                                                                  |

|                      |            |          | sun4v defines the minimum default value to be 13 if this property is not specified in a cpu node.                                                                                                                                                                                                                                                                             |

| mmu-#shared-contexts | PROP_VAL   | no       | A 64-bit unsigned integer giving the number of primary and<br>secondary shared context registers supported by this virtual<br>CPU's MMU. If not present the default value is assumed to<br>be 0                                                                                                                                                                               |

| mmu-#va-bits         | PROP_VAL   | no       | A 64-bit unsigned integer giving the number of virtual<br>address bits supported by this virtual CPU. If not present a<br>default value of 64 is assumed.                                                                                                                                                                                                                     |

|                      |            |          | Note: It is legal for there to be fewer VA bits than real address bits.                                                                                                                                                                                                                                                                                                       |

| mmu-compatible       | PROP_DATA* | no       | String array listing alternate mmu-type values that this virtual CPU's MMU interface is also compatible with                                                                                                                                                                                                                                                                  |

| mmu-max-#tsbs        | PROP_VAL   | no       | A 64-bit unsigned integer giving the maximum number of<br>TSBs this virtual CPU can simultaneously support. If not<br>present the default value is assumed to be 1.<br><i>Note: sun4v Solaris assumes at least 2 are available.</i>                                                                                                                                           |